# A Full Adder Design with CNFETs for Real Time, Fault Tolerant and Mission Critical Applications

Jitendra Kumar Saini, Avireni Srinivasulu, and Renu Kumawat

Abstract—The VLSI based circuits often pose challenges in the form of various faults (such as transient faults, permanent faults, stuck-at-faults). These faults appear even after testing also. They occur because of reduction in the size of the circuit or during real-time implementation, as these faults are difficult to detect. It is very important to detect and rectify all such faults to make the system foolproof and achieve expected functionality. In this paper, 12 transistors based, full adder circuit (12T-FAC) using Carbon Nanotube Field Effect Transistor (CNFET) technology is proposed. The proposed design based on CNFET provides high fault resistance towards transient, permanent faults and works with least power, delay and power-delay product (PDP). Later, features like fault detection and correction circuit have been added in 12T-FAC. The final version of full adder circuit capable of correcting errors has been used in designing applications like multipliers. The proposed full adder circuit was designed with CNFET technology, simulated at 32 nm with supply voltage +0.9 V using the Cadence Virtuoso CAD tool. The model used is Stanford PTM.

Keywords—CNFET, Full Adder, Fault Detection Full Adder, Fault Correction Full Adder, Multiplier.

Original Research Paper DOI: 10.7251/ELS2024066S

#### I. Introduction

In the real-time circuits, it is crucial to identify faults else the outcome may be catastrophic for the system and may even claim human lives too. While designing circuits for these applications, fault detection and fault correction have played a crucial role and posed challenges [1]. As Moore's Law states, "The number of transistors in dense integrated circuit doubles every two years", and hence leads to the growth of complexity. The efforts to bring down the size of the circuits have also made the later prone to certain faults like crosstalk, noise, etc. There are other setback issues which remain undetected during

Manuscript submitted for review on 8 September, 2020. Received in revised form on 25 November, 2020. Accepted for publication 27 November, 2020.

Jitendra Kumar Saini is with the Department of Electronics and Communication Engineering, Manipal University Jaipur, Jaipur-303007, INDIA (e-mail: jitendraksaini@bitmesra.ac.in).

Avireni Srinivasulu, Senior Member, IEEE, is with the Department of Electronics and Communication Engineering, JECRC University, Jaipur-303905, Rajasthan, INDIA. (E-mail: avireni@jecrcu.edu.in (or) avireni@ieee. org).

Renu Kumawat is with the Department of Electronics and Communication Engineering, Manipal University Jaipur, Jaipur-303007, INDIA (e-mail: renu. kumawat@jaipur.manipal.edu).

the initial testing. These issues are often difficult to detect and more concerned for its rectification and therefore the majority of the researchers usually concentrate on the identification and rectification of such issues [2]. The integrated circuits can be designed using various components like adder being the most common among the preferred by the designers. An adder is the simplest component capable of executing an arithmetic operation. It can be used to design various similar arithmetic and logical circuits [3].

The applications where carbon nanotubes may be used are antennas, invasive nanobots, miniaturized satellites, and Geo-positioning systems [4]. But there are applications where an alternate to resistors may work more effectively in optics based devices wherein Chlorophyll like organic semiconductors such as phthalocyanines (CuPc) with good thermal stability, chemical stability, light resistance, temperature resistance, coating strength and resistance to bases is preferred [4]-[5]. Some such applications are temperature sensors, humidity sensors, photo detectors, solar cells, optoelectronic devices, radio frequency identification, etc [5]. For these applications, the real-time systems need on-the-fly fault detection and correction circuits to make a system truly fault-tolerant. [5]

In VLSI, adders are used extensively and hence while designing a circuit using CNFET [6], adders are an obvious choice.

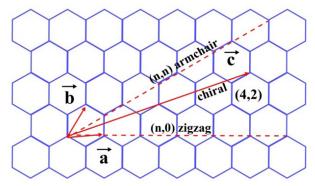

Carbon nanotube (CNT) is an allotrope of carbon with a cylindrical structure. The structure is found to be either single-walled carbon nano tube (SWCNT) or multi-walled carbon nano tube (MWCNT). SWCNT is a single sheet rolled up cylindrically along a wrapping vector  $C = n_1 \mathbf{a} + n_2 \mathbf{b}$ , where  $n_1$  and  $n_2$  are positive integers which specify the Chirality of the tube, and 'a' and 'b' are lattice unit vectors, as shown in Fig. 1.

Fig. 1. A spread-out sheet of graphite and Chirality of the CNT tube [8]

Depending upon the value of  $n_1$  and  $n_2$ , SWCNT can be either metallic or semiconducting. If the  $n_1$ - $n_2$  is a multiple of 3,

SWCNT is metallic or else it is semiconductor. Further classification of SWCNT includes armchair CNT  $(n_1 = n_2 = n)$ , zigzag CNT  $(n_1 = n, n_2 = 0)$  and Chiral CNT  $(n_1 \neq n_2 \text{ and } n_p, n_2 \neq 0)$ . The armchair CNTs conductors while zigzag and Chiral CNT's act as either semiconductor or conductor depending upon the difference in indices (i.e.  $n_1 - n_2$ ) [7]-[8].

The expression for the threshold voltage  $(V_{th})$  [7], equivalent to half the band gap of CNFET is shown in (1):

$$V_{th} \approx E_{bg} / 2e \approx 0.436 / D_{CNT}(nm)$$

(1)

Where the  $E_{bg}$  is the band gap of CNFET, e is the electron charge,  $D_{CNT}$  is the diameter of carbon nanotubes as given in (2):

$$D_{CNT} = d \approx 0.0783 \sqrt{n_1^2 + n_2^2 + n_1 n_2}$$

(2)

The thermal efficiency (Z) of the circuit as given in (3) is improved using nano-structuring and bandgap engineering by reducing the lattice thermal conductance and enhancing the Seebeck coefficient [9]. CNT based applications typically offer superior potential where the CNTs increase the power factor with increasing temperature [9].

Efficiency (Z) is calculated from expression [10]:

$$Z = \frac{\sigma \alpha^2}{K} \tag{3}$$

where,  $\sigma$  is the electrical conductivity, k is the thermal conductivity and  $\alpha$  is the Seeback coefficient. Later a dimensionless figure of merit came into existence which is calculated as ZT.

Temperature (T) as shown in (4) is calculated from expression [10]:

$$T = \frac{T_1 + T_2}{2} \tag{4}$$

where, T<sub>1</sub> and T<sub>2</sub> are the temperature of two contacts. The above equations are applicable for fabricating power generation devices using Bi,Te<sub>3</sub> and CNT along with silicon adhesive.

Section II and III of theresearch article discuss the existing full adder circuit designs and fault tolerant circuit designs approaching all along the drawbacks. Section IV discusses the proposed design. Section V gives the simulation results, comparative details and finally Section VI give concluding remarks.

# II. Existing Full Adde R Circuit Designs

The conventional full adder design [3] consists of 28 transistors and has a larger propagation delay due to the presence of 5 transistors in the output data path. Transmission Gate Adder (TGA) works on transmission gate logic, has a transistor count of 20 and critical data path delay of 4 transistors. This design has a drawback in driving capability [3]. Transmission Function Adder (TFA) carrying 16 transistors works on the principle of the transmission function theory. Similarly TGA and TFA also suffer in its driving capabilities [11].

In the case of Complementary Pass-transistor Logic Transmission Gate (CPL-TG), this design has better driving abilities but however it uses more transistors [12]. Mirror full adder design is an alternative to C-CMOS based full adder circuit. Mir-

ror adder uses Pass Transistor Logic (PTL) approach that has a critical path of 4 transistors. Thus, it results in faster full adder design and lower power delay product along with a high transistor count [13]. Static Energy Recovery Full Adder (SERF) uses only 10 transistors, but suffers from a threshold loss of problem [14]. The 13A full adder circuit uses 10 transistors similar to SERF full adder design and suffers from a specific problem of output voltage level degradation [15]. Hybrid Pass Transistor Logic with Static CMOS output drive (HPSC) full adder is designed using transmission gate logic, pass transistor logic and CMOS logic with a transistor count of 26 [16]. NEW-HP-SC full adder consists of 24 transistors and has higher power consumption because it has one extra inverter in the full adder design [17]. Complementary and level restoring carry logic full adder (CLRCL) is based on pass transistor logic and uses only 10 transistors. In this case, power consumption is more due to the presence of inverter circuit in the design of a full adder [18]. The Ours1 full adder consists of double pass-transistor logic (DPL) and that uses 28 transistors in the circuit of full adder. This design suffers from poor driving capability [19]. Hybrid CMOS logic with transmission gate logic full adder (HCTG) consists of 16 transistors and has a critical path delay of 4 transistors. One important drawback in HCTG is that it is not suitable for cascaded stages because it has poor driving capability due to the coupling of inputs and outputs [20]. Removed Single Driving Full Adder (RSD-FA) consists of 26 transistors. This design has an XOR/XNOR circuit that exhibits full driving capability and output delay path of 4 transistors. RSD-FA provide lower power consumption as well as the high speed at the cost of more transistor count [21]. In 1-Bit full adder with 18 transistors [22], five inverters are used that is three at primary inputs and 2 in the intermediate stage which results in poor driving capability. Hybrid Multi-Threshold Full Adder (HMTFA) consists of 23 transistors. Provides Critical path of 4 transistors and experience a threshold problem due to the use of more number of inverters [23].

Literature review of full adders has been verified with different logic families. They are found to vary in their characteristic features, performance, power consumption and propagation delay. The crucial points undermining the approximation and comparison of performance among the devices are delay, power consumption, and power-delay product. Circuit delay along with other factors is largely on account of number of transistors consecutively connected in series all along the channel width and intra-cell wiring capacitances. Similarly, size is directly proportional to the number of transistors and results into complexity while implementation. Thus, by reducing the number of transistors, we can optimize the circuit performance in terms of area and speed.

This paper demonstrates the improvement in circuit performance by reducing the number of transistors and length of the critical path of outputs. One-bit full adder circuit using 12 CN-FETs (denoted as 12T-FAC) has been proposed in this paper. In the proposed full adder circuit, care has been taken to minimize the limitations of the earlier proposed full adder and also to improve the overall circuit performance.

#### III. EXISTING FAULT-TOLERANT CIRCUIT DESIGNS APPROACH

Any fault tolerant system needs to acquire few characteristics by virtue of its design, existing design approaches like redundancy (time, hardware), etc. are summed up to get the features at a glance. Here on Time Redundant design approach deals with fault detection by executing the same operation on two circuits which are identical and at times by adding latency in the input feed of one of the circuits and compare the output thus obtained, where the same output represents no fault and the difference of output represents a defaulted circuit [1]. The Hardware Redundancy design approach requires multiple instances (two, three or more) of the identical circuits with common input feed giving out different results [2]. Operand Width Aware Hardware Reuse design approach uses the combination of the static and dynamic (redundant) adder to design ALUs. The Self-Checking Carry Select Adder design [24] approach detects single bit fault at run time and also capable of detecting a stuck-at fault. Self-Repairing Adder [25] design approach makes use of a pre-defined rule which says, "For 3 input adders, same input values should produce the same output values and if any of the input is flipped, the output differs". The Real-Time Fault Tolerant Full Adder design approach moves one step ahead and is capable of detection and correction of single and double faults at run time [26].

Every technique has got its own advantages and disadvantages like time redundant design approach is unable to detect faults if the results of the initial input feed are incorrect [27]. This approach does not detect stuck-at-faults. In hardware redundant design approach real-time faults and stuck-at faults may not be possible to detect, hence correction circuit cannot be designed, and also there will be a drasticincrease in size of the circuit [28]. In Operand Width Aware Hardware Reuse design approach the computational complexity, power consumption, and fault propagation are the challenges that designers need to address [29]. The Self Checking Carry Select Adder design approach [30] suffers from a probable handicap to detect the fault site if there are multiple faults detected in the circuit. It also restricts its use in self-correcting circuits. The Self Repairing Adder design approach [31] fails while multiple wrong inputs are provided to the adder and are unable to identify the location. In Real-Time Fault-Tolerant Full Adder design approach the number of hardware components is high due to redundancy in design and thus are more costly [32]-[33]. Due to the redundant circuit design, critical path delay is increased and thereby increases the overall circuit delay [34]-[38].

The proposed design of full adder circuit (12T-FAC) along with error detection and correction circuit mechanism deals with delay, reduces the redundant components, identifies stuckat-fault, can also detect multiple fault locations and is capable of fault corrections. Hence, fabrication of the proposed design, true real-time fault tolerant circuit design can be achieved [39]-[42].

## IV. PROPOSED DESIGN

The proposed system is verified on the basis of the criteria given below:

- Test Strategy: We have tested the output under two functional units considering each output (Sum and Carry) to be independent of the other. This strategy allows us to trace back the fault location.

- Hardware Design: The circuit reduces the need for redundant adders and it does not make use of multiple rail checkers which allows a comparatively lean hardware design.

- Fault Detection: Proposed design is fully capable of fault detection and fault correction in case of sporadically occurring transient and other permanent faults.

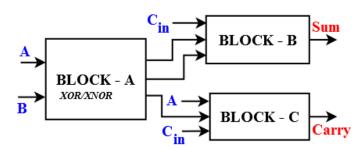

The block diagram of the proposed 1-bit adder circuit as represented in Fig. 2 contains three blocks, wherein, Block-A takes input A and B to produce intermediate output as XOR/XNOR signal pair. This block is implemented using transistors  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_8$ ,  $C_9$ , and  $C_{10}$ . Block-B is a Pass Transistor Logic implementation that takes intermediate output XOR/XNOR as input along with initial carry  $C_{in}$  (if any) and generates output Sum. Block-B is implemented using  $C_4$ ,  $C_5$ ,  $C_6$ , and  $C_{11}$ . Block-C is a multiplexer that takes A, XNOR, and  $C_{in}$  as input and produces Carry as output. Block-C is implemented using transistors  $C_7$  and  $C_{12}$ .

Fig. 2. Block diagram of proposed 12T-FAC

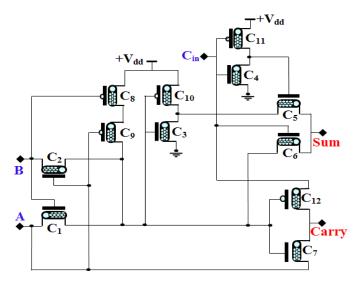

Fig. 3. Schematic of proposed 12T-FAC implemented using CNFET.

The proposed 12 transistors full adder circuit using CNFET is shown in Fig. 3. The proposed 12T-FAC circuit has a critical path delay of 3 and provides full output voltage swing. The Sum and Carry equation of 12T-FAC are:

$$Sum = A \oplus B \oplus C_{in}$$

(5)

$$Sum = \overline{ABC_{in}} + \overline{ABC_{in}} + A\overline{BC_{in}} + ABC_{in}$$

(6)

$$Sum = (AB + \overline{AB})C_{in} + (A\overline{B} + \overline{AB})\overline{C_{in}}$$

(7)

$$Carry = (\overline{AB} + \overline{AB})C_{in} + A(\overline{AB} + AB)$$

(8)

$$Carry = (A\overline{B} + \overline{AB})C_{in} + AB$$

(9)

Using (2) the value of  $D_{CNT}$  was calculated keeping the value of  $n_2 = 0$  and varying value of  $n_1$  in the range of 7-19 with step size 2.

$$D_{CNT} = 0.0783 * n_1 \tag{10}$$

Similarly, using (1) and the various  $D_{\it CNT}$  values, the value of  $V_{\it th}$  was calculated as

$$V_{th} = 0.436 / D_{CNT} \tag{11}$$

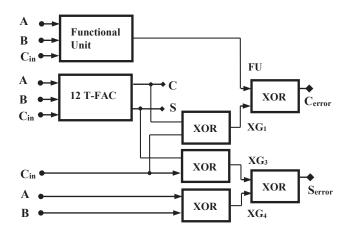

Using 12T-FAC, the Fault Detection Full Adder (FDFA) circuit based on CNFET is proposed. This circuit is capable of detecting multiple faults (single and double) in real-time along with identification of fault site. The schematic of the FDFA is shown in Fig. 4.

Fig. 4. Schematic of FDFA

Proposed FDFA makes use of 3 input  $(A, B, C_{in})$  and generates 4 output  $(S, C, S_{error}, C_{error})$  where S and C denotes actual results (i.e. Sum and Carry) of FDFA and  $S_{error}$  and  $C_{error}$  verifies whether there is an error in the sum or carry outputs of FDFA respectively.  $C_{error}$  is generated by XOR of  $XG_1$  and Functional Unit (FU) given in (12) whereas, intermediate output stage FU and  $XG_1$  are shown in (12) and (13) respectively.

$$FU = \overline{(A + B + \overline{C_{in}})(\overline{A} + \overline{B} + C_{in})}$$

(12)

$$XG_1 = C \oplus C_{in}$$

(13)

$$C_{error} = FU \oplus XG_1 \tag{14}$$

When  $C_{error} = '0'$ , indicates fault-free FDFA circuit while  $C_{error} = '1'$ , indicates the faulty FDFA circuit and the fault site is the carry output stream.

Similarly, in regards to the detection of a fault, if fault site is in the sum output stream that requires 3 XOR gates.  $S_{error}$  is generated by XOR of  $XG_3$  and  $XG_4$  shown in (17) whereas, intermediate output stage  $XG_3$  and  $XG_4$  are shown in (15) and (16) respectively.

$$XG_3 = C_{in} \oplus S \tag{15}$$

$$XG_4 = A \oplus B$$

(16)

$$S_{error} = XG_3 \oplus XG_4 \tag{17}$$

When  $S_{error} = '0'$ , indicates fault-free FDFA circuit, while  $S_{error} = '1'$ , indicates the faulty FDFA circuit and the fault site is the sum output stream. These would make it capable of detecting single or multiple faults occurring in sum and carry bits and when no error occurs, then  $S_{error}$  and  $C_{error}$  will remain Zero representing fault free FDFA.

Once the fault site is identified, the proposed FDFA makes use of Fault Correction Full Adder (FCFA) for recovery of erroneous input in real-time. This circuit design deal with all the sporadically occurring transient faults and permanent hardware faults thus make the circuit a real fault-tolerant design.

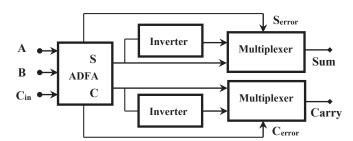

In this approach, an inverter is used along with multiplexer to correct the output sum and carry, instead of using standby adder to replace the faulty adder as is used in earlier approaches. This substantially reduces the hardware size to a fraction as compared to the other existing design approaches. The schematic of the FCFA is shown in Fig. 5.

Fig. 5. Schematic of proposed FCFA.

The output (S and S) generated by the 12T-FAC from input (S, S) is fed to the FDFA circuit which produces output (S, S) to be further fed to FCFA, which takes S, S and their complements as input and passes to the Multiplexer where S0 and S1 are used as select line, depending upon the detection of error output the Sum and Carry are selected.

If the outputs  $S_{error}$  and  $C_{error}$  are 0, then the S and C outputs of FDFA are directly transferred as final Sum and Carry of FCFA with the help of multiplexer and if  $S_{error}$  and  $C_{error}$  of FDFA are 1, then the inverted outputs received from the inverter gets selected by multiplexer and are transferred as final Sum or Sum and Carry or Carry of FCFA.

#### V. SIMULATION RESULTS AND COMPARISON

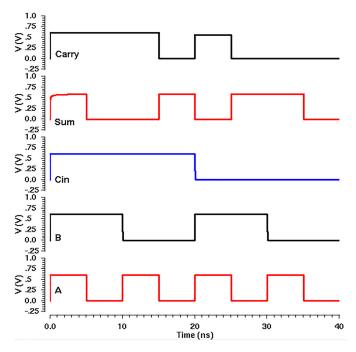

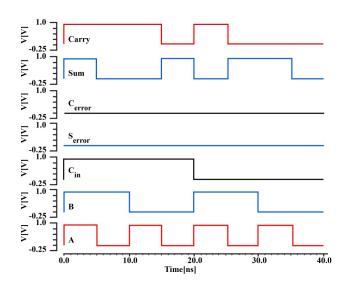

The simulation is carried out using the Cadence Virtuoso Tool. The circuit is designed with CNFET 32 nm technology [43] at Supply Voltage  $(+V_{dd})$  0.9 V. The waveform of the 12T-FAC consists of inputs (A, B,  $C_{in}$ ) and outputs (Sum and Carry) are shown in Fig. 6.

TABLE I

COMPARISON BETWEEN PROPOSED 12T-FAC AND OTHER FULL ADDERS IN

TERMS OF TRANSISTOR COUNT, DELAY, POWER AND PDP.

| Full Adder    | Transistor<br>Count | Power (µW) | Delay (ps) | PDP (aJ) |

|---------------|---------------------|------------|------------|----------|

| C-CMOS [3]    | 28                  | 0.124      | 12.355     | 1.532    |

| TGA [3]       | 20                  | 0.135      | 10.104     | 1.364    |

| TFA [11]      | 16                  | 0.109      | 11.701     | 1.275    |

| SERF [14]     | 10                  | 3.326      | 9852.7     | 32770.0  |

| 13A [15]      | 10                  | 5.819      | 9507.8     | 55325.8  |

| NEW-HPSC [17] | 24                  | 0.123      | 30.232     | 3.718    |

| CLRCL[18]     | 10                  | 5.903      | 231.18     | 1364.6   |

| RSD-FA [21]   | 26                  | 0.091      | 9.427      | 0.857    |

| 18T-FA [22]   | 18                  | 0.088      | 8.93       | 0.785    |

| HMTFA [23]    | 23                  | 0.121      | 16.909     | 2.056    |

| This work     | 12                  | 0.039      | 6.876      | 0.268    |

The simulation results of all the full adders as reported in Section 2 and proposed 12T-FAC are summarized in Table I. However, the supply voltage ( $+V_{DD}$ ) is varied in the range of 0.6 V to 1.4 V with a step size of 0.1 V to verify the fault tolerance of the circuit in varying voltage scenario. It was observed that the proposed circuit performs consistently under variations in various parameters, as could be seen in Table II.

Fig. 6. Waveform of proposed 12T-FAC using CNFET

TABLE II COMPARISON OF PROPOSED 12T-FAC DESIGN IN TERMS OF VARIATION IN  $V_{\rm DD}$  Supply from 0.6 V to 1.4 V for 32 nm CNFET Technology with  $$\rm V_{TH}=0.289~V.$$

| Proposed Full<br>Adder | V <sub>DD</sub> (Volts) | 12T-FAC               |

|------------------------|-------------------------|-----------------------|

|                        | 0.6                     | 0.018 μW              |

|                        | 0.7                     | $0.022~\mu W$         |

|                        | 0.8                     | $0.029~\mu\mathrm{W}$ |

|                        | 0.9                     | $0.039~\mu\mathrm{W}$ |

| Average Power          | 1.0                     | $0.059~\mu\mathrm{W}$ |

|                        | 1.1                     | $0.076~\mu\mathrm{W}$ |

|                        | 1.2                     | $0.095~\mu\mathrm{W}$ |

|                        | 1.3                     | 0.119 μW              |

|                        | 1.4                     | $0.166~\mu W$         |

|                        | 0.6                     | 9.353ps               |

|                        | 0.7                     | 8.019ps               |

|                        | 0.8                     | 7.821ps               |

|                        | 0.9                     | 6.876ps               |

| Delay                  | 1.0                     | 6.772ps               |

|                        | 1.1                     | 6.701ps               |

|                        | 1.2                     | 6.559ps               |

|                        | 1.3                     | 6.498ps               |

|                        | 1.4                     | 6.339ps               |

|                        | 0.6                     | 0.168aJ               |

|                        | 0.7                     | 0.176aJ               |

|                        | 0.8                     | 0.227aJ               |

|                        | 0.9                     | 0.268aJ               |

| PDP                    | 1.0                     | 0.400aJ               |

|                        | 1.1                     | 0.509aJ               |

|                        | 1.2                     | 0.623aJ               |

|                        | 1.3                     | 0.773aJ               |

|                        | 1.4                     | 1.052aJ               |

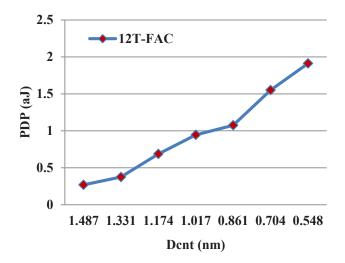

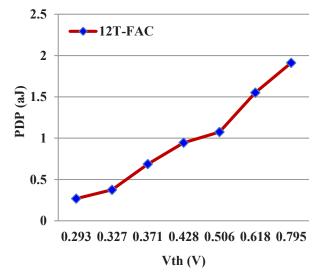

Fig. 7. PDP Versus Dcnt Variations for proposed circuit

The results from (10) and (11) are used to plot parameter variation of power-delay product (PDP) of 12T-FAC with CN-FET diameter ( $D_{CNT}$ ) and threshold voltage ( $V_{th}$ ) as shown in Figs. 7 and 8, respectively.

The CNT structure used is SWCNT in Zigzag orientation where  $(n_1 = n, n_2 = 0)$ . For simulation and study purpose, the value of n1 was varied in the range of 7 to 19. Significant PDP results were observed at  $n_1 = 19$  and hence the value was used for further comparisons. Other CNFET parameters used during the simulation are shown in Table III.

Fig. 8. PDP Versus Vth Variations for proposed circuit.

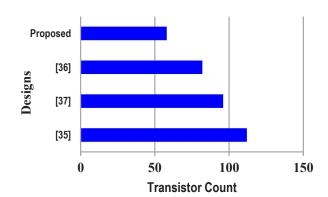

Fig. 9. Comparison of fault tolerant design with transistor count.

TABLE III

CNFET DESCRIPTION, VALUE AND ITS PARAMETER.

| Description                                          | Value  | CNFET<br>Parameter |

|------------------------------------------------------|--------|--------------------|

| Physical channel length                              | 32 nm  | Lg                 |

| The mean free path in the intrinsic CNT channel      | 200 nm | Lgeff              |

| The length of doped CNT source-side extension region | 32 nm  | Lss                |

| The length of doped CNT drain-side extension region  | 32 nm  | Ldd                |

| The Fermi level of the doped S/D tube                | 6 EV   | Efi                |

| Description                                                           | Value   | CNFET<br>Parameter |

|-----------------------------------------------------------------------|---------|--------------------|

| The dielectric constant of high-k top gate dielectric material        | 16      | Kgate              |

| The thickness of high-k top gate dielectric material                  | 4 nm    | Tox                |

| The coupling capacitance between the channel region and the substrate | 20 pf/m | Csub               |

| Distance between the tubes                                            | 20 nm   | Pitch              |

| 7: \$4                                                                | 19      | n1                 |

| Zigzag Structure                                                      | 0       | n2                 |

| Number of CNT tubes                                                   | 3       | CNTPos             |

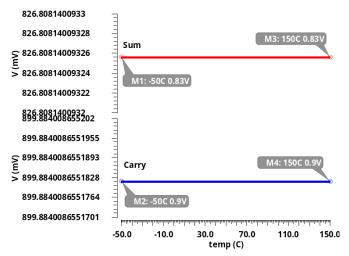

The impact of temperature variations on the proposed 12T-FAC circuit was observed from the simulations for the temperature range -50°C to 150°C. The simulated temperature stability was observed to be 0.00000035%, as shown in Fig.10.

Fig. 10. Simulated temperature stability 12T-FAC

The static power consumption is determined by the clock and all other inputs that are connected with the low logic to check the leakage current.

The dynamic power dissipation is calculated using switching frequency and external load capacitance from relation [5]:

$$P_{\text{dynamic}} = \alpha C_L f V_{DD}^2$$

(18)

where  $\alpha$  ( $0 \le \alpha \le 1$ ) is switching activity factor, f is the clock frequency and  $C_L$  is the load capacitance. The frequency and capacitance are directly proportional to the dynamic power consumption.

To find the static power and leakage current,  $V_{DD}=0.9\mathrm{V}$  is supplied with low level inputs (A, B, Cin), whereas to calculate total power consumption  $V_{DD}=0.9\mathrm{\ V}$  is supplied with inputs (A, B, Cin). When these parameters were applied to simulate the proposed 12T-FAC leakage current, static power, dynamic power, and total power recorded were 0.275 nA, 0.256 nW, 38.979 nW, and 39.235 nW, respectively.

The average power consumption of 1-bit FCFA was found to be 9.81 nW and delay was 5.382 ps. The power-delay prod-

uct was 0.0528 aj. The circuit thus designed when simulated along with existing designs, was found to be at-par in terms of capabilities like fault detection and fault correction. Also, it is evident that the proposed design reduces the number of transistors by 30% and the size by 45% approximately as depicted in Fig. 9.

$\label{thm:table} \begin{tabular}{ll} TABLE~III\\ CNFET~Description,~Value~And~Its~Parameter. \end{tabular}$

| Description                                                           | Value   | CNFET     |

|-----------------------------------------------------------------------|---------|-----------|

| Description                                                           |         | Parameter |

| Physical channel length                                               | 32 nm   | Lg        |

| The mean free path in the intrinsic CNT channel                       | 200 nm  | Lgeff     |

| The length of doped CNT source-side extension region                  | 32 nm   | Lss       |

| The length of doped CNT drain-side extension region                   | 32 nm   | Ldd       |

| The Fermi level of the doped S/D tube                                 | 6 EV    | Efi       |

| The dielectric constant of high-k top gate dielectric material        | 16      | Kgate     |

| The thickness of high-k top gate dielectric material                  | 4 nm    | Tox       |

| The coupling capacitance between the channel region and the substrate | 20 pf/m | Csub      |

| Distance between the tubes                                            | 20 nm   | Pitch     |

| 7. oraca Stanistana                                                   | 19      | n1        |

| Zigzag Structure                                                      | 0       | n2        |

| Number of CNT tubes                                                   | 3       | CNTPos    |

Table IV gives the capability comparison with the existing design approaches. At the time of simulation, it has been observed that the proposed circuit of FCFA is successfully able to auto correct the error, if any. From Fig. 11, it can be seen that the input sequence  $(A, B, C_{in})$  without any error  $(S_{error} = C_{error} = 0)$  gives expected output for various input combinations.

TABLE IV

CAPABILITY COMPARISON WITH EXISTING DESIGN APPROACHES.

| Designs                           | [31]                                            | [33]                                                                                        | [32]                                                                      | Proposed                                                                  |

|-----------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Individual<br>transistor<br>count | 2-Adder 56<br>4-XNOR 24<br>2-Eqt 24<br>2-Mux 08 | 1-Adder 28<br>2-XNOR 10<br>2 AND 14<br>1 OR 6<br>1-Fun.Unit 14<br>2-Mux 08<br>8-Inverter 16 | 1-Adder 28<br>5-XNOR 30<br>1-Fun. Unit 12<br>2-Mux 08<br>2-Inverter 04    | 1-Adder 12<br>5-XOR 20<br>1-Fun. Unit 18<br>2-Mux 04<br>2-Inverter 04     |

| Total<br>number of<br>transistors | 112                                             | 96                                                                                          | 82                                                                        | 58                                                                        |

| Fault<br>coverage                 | Single net<br>Multi net<br>Single fault         | Single net<br>Multi net<br>Single fault<br>Double fault<br>Stuck-at fault                   | Single net<br>Multi net<br>Single fault<br>Double fault<br>Stuck-at fault | Single net<br>Multi net<br>Single fault<br>Double fault<br>Stuck-at fault |

| Fault repairing                   | Not possible in case of double fault            | Possible in all cases                                                                       | Possible in all cases                                                     | Possible in all cases                                                     |

| Designs                               | [31]   | [33] | [32] | Proposed        |

|---------------------------------------|--------|------|------|-----------------|

| Output<br>reliability<br>single fault | 100%   | 100% | 100% | 100%            |

| Output<br>reliability<br>double fault | 85.82% | 100% | 100% | 100%            |

| Technology                            | CMOS   | CMOS | CMOS | CMOS/<br>CNTFET |

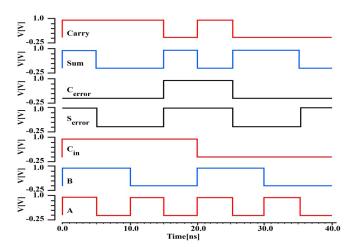

Fig. 11. Output waveform of FCFA with no error.

Fig. 12. Output waveform of FCFA with error correction in Sum and Carry

In Fig. 12, the observed output from input sequence (A, B,  $C_{\rm in}$ ) with fault detected in  $S_{\rm error}$  and  $C_{\rm error}$  of 12T-FAC shows the capability to auto correct the fault in final Sum and Carry. Further, to test the performance of FCFA in complex circuits, multiplier is designed in both CMOS and CNFET technology as dipicted in Table V.

|            | TA | BLE V   |     |         |  |

|------------|----|---------|-----|---------|--|

| COMPARISON | OF | мпптірі | IFD | DESIGNS |  |

| Multipliers                          | Power<br>(µW) | Delay<br>(ps) | PDP (aj) | Technology<br>(nm) |

|--------------------------------------|---------------|---------------|----------|--------------------|

| 4 BIT Multiplier [32]                | 94.38         | 598.3         | 56467.6  | CMOS 55            |

| Proposed 4 BIT Multi-<br>plier CMOS  | 24.21         | 418.3         | 10127.0  | CMOS 45            |

| Proposed 4 BIT Multi-<br>plier CNFET | 2.884         | 303.4         | 875.006  | CNFET 32           |

| 8 BIT Multiplier [32]                | 712           | 1326          | 944112   | CMOS 55            |

| Proposed 8 BIT Multi-<br>plier CMOS  | 498           | 987.3         | 491675.4 | CMOS 45            |

| Proposed 8 BIT Multi-<br>plier CNFET | 21.75         | 672.4         | 14624.7  | CNFET 32           |

#### VI. CONCLUSION

In this paper, we have proposed a Full Adder Circuit (12T-FAC) using CNFET, Fault Detection Full Adder (FDFA) Circuit using CNFET, Fault Correction Full Adder (FCFA) Circuit using CNFET, 4-bit and 8-bit multiplier circuit using FCFA and CNFET.

The 12T-FAC is optimized to consume less power, having lesser delay and that too with less than the average number of transistors when compared with other similar designs. The proposed design is capable of performing all the tasks its peers are capable of. The FDFA and FCFA are the functionality extensions of proposed 12T-FAC to detect and correct the input/output. Finally, to test this circuit for its scope, capabilities, and worthiness, it was used to design a multiplier application.

It can also be seen from the simulation results that the Adders and Multipliers thus designed are producing better results as compared to other prevalent designs of a full adder. Table IV shows that the proposed ACFA design reduces the number of transistors required by 30% and the size by approximately 45%. Also, when the application (multiplier) was compared with other similar multiplier designs, the power consumption was found to be substantially low and so the delay. The proposed design deals with faults in real time and performs corrective action, this enables us to conclude that the proposed 12T-FAC is a better-suited design and a choice for future applications.

## REFERENCES

- C. Khedhiri, M. Karmani, B. Hamdi, KaLok Man, "Concurrent error detection adder based on two paths output computation", in proc. of IEEE International Symposium on parallel and Distributed Processing with Applications Workshops (ISPAW), pp. 27 – 32, (2011). DOI:10.1109/ ISPAW.2011.63

- [2] D. Siewiorek and R. Swarz, Reliable Computer Systems: Design and Evaluation, Digital Press, (2014).

- [3] N. H. E. Weste and K. Eshraghian, Principles of CMOS VLSI Design: A System Perspective MA, USA: Addison-Wesley, (1988).

- [4] A. Chauhan, L. Mahor, P.Tiwari, "Low Power Quaternary Adder Using CNFET", in proc. of IEEE VLSI Device Circuit and System (VLSI DCS) 2020, 18-19 July 2020, Kolkata, India, DOI: 10.1109/ VLSIDCS47293.2020.9179898.

- [5] C. Ravariu, D. E. Mihaiescu, A. Morosan, L. Georgeta -Alecu, D.

- Istrati, Gated resistors with copper phthalocyanine films, Journal of Optoelectronics and Advanced Materials, vol. 22, no. 3-4, pp.171-175 (2020).

- [6] J. Deng and H. S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application-Part I: Model of the intrinsic channel region," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3186–3194, (Dec. 2007). DOI: 10.1109/TED.2007.909030.

- [7] J. Deng and H. S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application-Part II: Full device model and circuit performance benchmarking," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3195–3205, (Dec. 2007). DOI: 10.1109/TED.2007.909043.

- [8] R. Saito, G. Dresselhaus, and M. S. Dresselhaus, Physical Properties of Carbon Nanotubes, Imperial College Press, London, (1998).

- [9] N. Fatima, Kh. S. Karimov, J.-Un Nabi, H.Meng, Z. Ahmad, M. Riaz, M. Mehran Bashir, M. Imran Khan, Rashid Ali, Adam Khan, FaridTouati, "Semi-transparent thermo-electric cells based on bismuth telluride and its composites with CNTs and grapheme", *Journal of Optoelectronics and Advanced Materials*, vol. 21, no. 5, pp. 333-337, (2019).

- [10] M. T. S. Chani, Kh. S. Karimov, KH. S. Karimov, Jameel-Un Nabi, A. Ahmed, I. Kiran, A. M. Asiri, "Fabrication and investigation of organic-inorganic semitransparent thermoelectric cells based on the composites of silicone-adhesive with Bi2Te3, graphene and carbon nanotubes", *Journal of Optoelectronics and Advanced Materials* vol. 21, no. 9, pp. 588-593, (2019)

- [11] N. Zhuang and H. Wu, "A new design of the CMOS full adder," *IEEE J. Solid-State Circuits*, vol. 27, no. 5, pp. 840–844, (May 1992). DOI: 10.1109/4.133177.

- [12] I. S. Abu-Khater, A. Bellaouar, and M. I. Elmasry, "Circuit techniques for CMOS low-power high-performance multipliers," *IEEE J. Solid-State Circuits*, vol. 31, no. 10, pp. 1535–1546, (Oct. 1996). DOI: 10.1109/4.540066.

- [13] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1079–1090, (Jul. 1997). DOI: 10.1109/4.597298.

- [14] R. Shalem, E. John, and L. K. John, "A novel low power energy recovery full adder cell," in Proc. 9th IEEE Great Lakes Symp. VLSI, (Feb. 1999), pp. 380–383. DOI: 10.1109/GLSV.1999.757461.

- [15] H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.* vol. 49, no. 1, pp. 25–30, (Jan. 2002). DOI: 10.1109/82.996055.

- [16] C.-H. Chang, J. Gu, and M. Zhang, "A review of 0.18-µm full adder performances for tree structured arithmetic circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 686–695, (Jun. 2005). DOI: 10.1109/TVLSI.2005.848806.

- [17] S. Goel, A. Kumar, and M. Bayoumi, "Design of robust, energy-efficient full adders for deep-sub micrometer design using hybrid-CMOS logic style," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 14, no. 12, pp. 1309–1321, (Dec. 2006). DOI: 10.1109/TVLSI.2006.887807.

- [18] J.-F. Lin, Y.-T. Hwang, M.-H. Sheu, and C.-C. Ho, "A novel high speed and energy efficient 10-transistor full adder design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 5, pp. 1050–1059, May 2007. DOI: 10.1109/TCSI.2007.895509.

- [19] M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for energy-efficient arithmetic applications," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 19, no. 4, pp. 718–721, (Apr. 2011). DOI: 10.1109/ TVLSI.2009.2038166.

- [20] P. Bhattacharyya, B. Kundu, S. Ghosh, V. Kumar, and A. Dandapat, "Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 23, no. 10, pp. 2001–2008, (Oct. 2015). DOI: 10.1109/TVLSI.2014.2357057.

- [21] Y. S. Mehrabani and M. Eshghi, "Noise and Process Variation Tolerant, Low-Power, High-Speed, and Low-Energy Full Adders in CNFET Technology," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 24, no. 11, pp. 3268-3281, (Nov. 2016). DOI: 10.1109/TVLSI.2016.2540071.

- [22] J. K. Saini, A. Srinivasulu and B. P. Singh, "A new low-power full-adder cell for low voltage using CNFETs", in proc. of IEEE International Conference on Electronics, Computers and Artificial Intelligence, Targoviste, Romania, 29 June-01 July, 2017, Pages-6. DOI: 10.1109/ ECAI.2017.8166425.

- [23] M. Maleknejad, S. Mohammadi, K. Navi, H. R. Naji and M. Hosseinzadeh "A CNFET-based hybrid multi-threshold 1-bit full adder design for energy efficient low power applications" *Int. J. of Electronics*, pp. 1-16, (June 2018). DOI: 10.1080/00207217.2018.1477205.

- [24] P. Reviriego, C. J. Bleakley and J.A. Maestro "Diverse Double Modular Redundancy: A New Direction for Soft-Error Detection and Correction", *IEEE Design & Test.* vol. 30 pp. 87-95, (April 2013). DOI: 10.1109/ MDT.2012. 2232964.

- [25] A. Ziv and J. Bruck, "Performance optimization of check pointing schemes with task duplication," *IEEE Transactions on Computers*, vol. 46, no. 12, pp. 1381-1386, 1997. DOI:10.1109/12.641939

- [26] D. P. Vasudevan, P. K. Lala and J. P. Parkerson, "Self-Checking Carry-Select Adder Design Based on Two-Rail Encoding," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 12, pp. 2696-2705, (2007). DOI: 10.1109/TCSI.2007.910537

- [27] A. Mukherjee, A.S. Dhar, "Real-time fault-tolerance with hot-standby topology for conditional sum adder", *Microelectronics Reliability*, vol. 55, no. 3, pp. 704–712, (2015). DOI: 10.1016/j.microrel.2014.12.011

- [28] A. Majumdar, S. Nayyar and J. S. Sengar, "Fault Tolerant ALU System," in proc. of International Conference on Computing Sciences, Phagwara, pp. 255-260, (2012). DOI:10.1109/ICCS.2012.36

- [29] M. Fazeli, A. Namazi, S.G. Miremadi, A. Haghdoost, Operand width aware hardware reuse: a low cost fault-tolerant approach to ALU design in embedded processors, *Microelectron. Reliab.*, vol. 51, no. 12, pp. 2374– 2387, (2011).

- [30] M. Valinataj "A novel self-checking carry look ahead adder with multiple error detection/correction" *Microprocessors and Microsystems*. pp. 38, (2014). DOI: 10.1016/j.micpro.2014.10.002.

- [31] M.A. Akbar, J.-A. Lee, Self-repairing adder using fault localization, Microelectronics Reliability, vol. 54, no. 6, pp. 1443–1451, (2014). DOI:10.1016/j.microrel.2014.02.033.

- [32] P. Kumar, R. K. Sharma, "Real-time fault tolerant full adder design for critical applications" *Engineering Science and Technology, an International Journal*, vol. 19, no. 3, pp. 1465-1472, (2016). DOI: 10.1016/j. jestch.2016. 05.001.

- [33] P. Kumar and R. K. Sharma, "Double fault tolerant full adder design using fault localization," in proc. of 3rd International Conference on Computational Intelligence & Communication Technology (CICT),

- Ghaziabad, pp. 1-6, (2017). DOI: 10.1109/CIACT.2017.7977345.

- [34] P. Kavitha, M. Sarada, K. Vijayavardhan, Y. Sudhavani and A. Srinivasulu, "Carbon nano tube field effect transistors based ternary Ex-OR and Ex-NOR gates", *Current Nanoscience*, vol. 12, no. 4, pp. 520-526, (Aug 2016). DOI: 10.2174/1573413712666151216221629.

- [35] A. Srinivasulu and K. Sivadasan, "Optical Exclusive-OR gate", Journal of Microwaves, Optoelectronics and Electromagnetic Applications, vol. 3, no. 1, pp. 20-25, (Apr 2003).

- [36] J. K. Saini, A. Srinivasulu and R. Kumawat, "High-Performance Low-Power 5:2 Compressor With 30 CNTFETs Using 32 nm Technology", International Journal of Sensors, Wireless Communications and Control, vol. 9, issue. 4, pp. 462-467, (2019). DOI: 10.2174/22103279096661902 06144601.

- [37] J. K. Saini, A. Srinivasulu, K. Renu, "Real-time Error Detectable Multiplier Circuit Using CNFET", Journal of Advanced Research in Dynamical and Control Systems, vol. 11, Issue. 07-SI, pp. 150-156, (2019), ISSN: 1943-023X.

- [38] J. K. Saini, A. Srinivasulu and R. Kumawat, "A Low Power High Speed CNTFETs Based Full Adder Cell With Overflow Detection", *Micro and Nanosystem*, vol. 11, no. 1, pp. 80-87, (2019), DOI: 10.2174 /1876402911666190211154634.

- [39] P. V. Lakshmi, M.Sarada, A.Srinivasulu and D. Pal, "Three Novel Single-Stage Full Swing 3-Input XOR", *International Journal of Electronics*, vol. 105, no. 8. pp. 1416-1432, (2018). DOI: 10.1080/00207217.2018.1460767

- [40] M.Sarada, A.Srinivasulu and D. Pal, "Novel Low-Supply, Differential XOR/ XNOR with Rail-to-Rail Swing, for Hamming-Code Generation", *International Journal of Electronics Letters*, vol. 6, no. 3. pp. 272-287, (2018), DOI: 10.1080/21681724.2017.1357761.

- [41] A.Srinivasulu, G.Sravanthi, M.Sarada and D. Pal, "FinFET based Miller-Encoder for UHF and SHF RFID application", *International Journal of Electronics*, vol. 105, no. 1. pp. 104-115, (2018), DOI: 10.1080/00207217.2017.1354401.

- [42] M. Sarada and A. Srinivasulu, "Self testing and fault secure XOR/XNOR circuit using FinFETs", in proc. of IEEE International Conference on Communication and Signal Processing, Melmaruvathur, Tamilnadu, India, pp. 976-980, Apr. 6-8, 2016. DOI: 10.1109/ICCSP.2016.77543.

- [43] http://nano.stanford.edu/model.php?id=23.